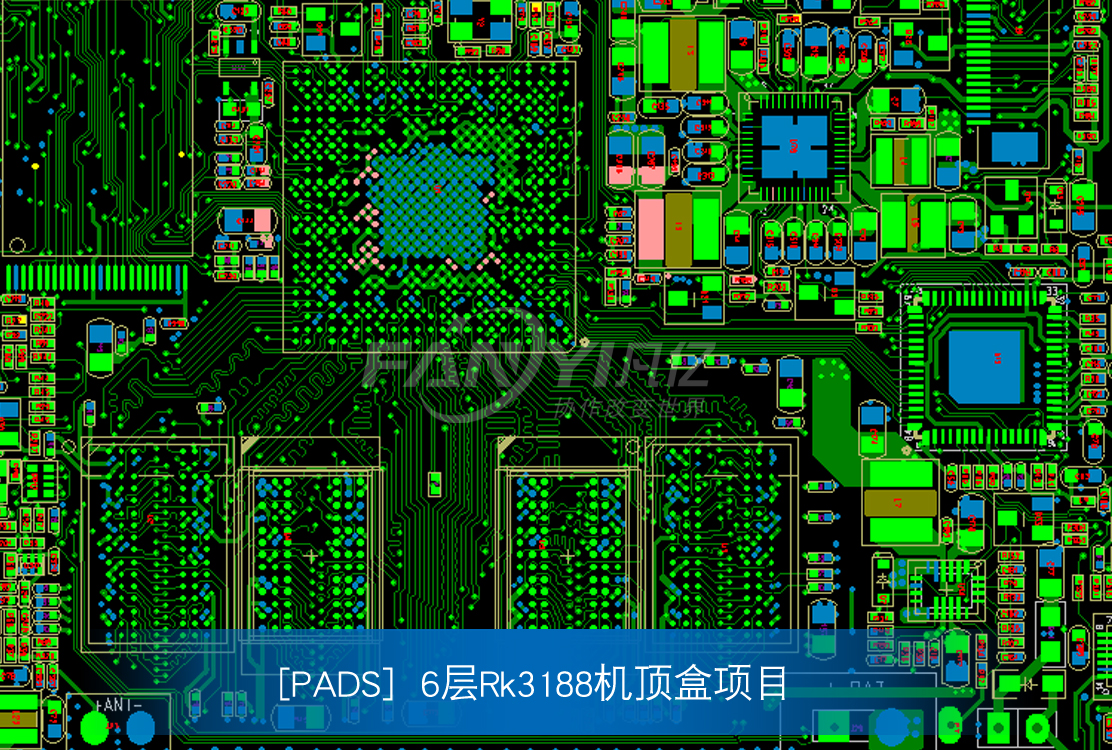

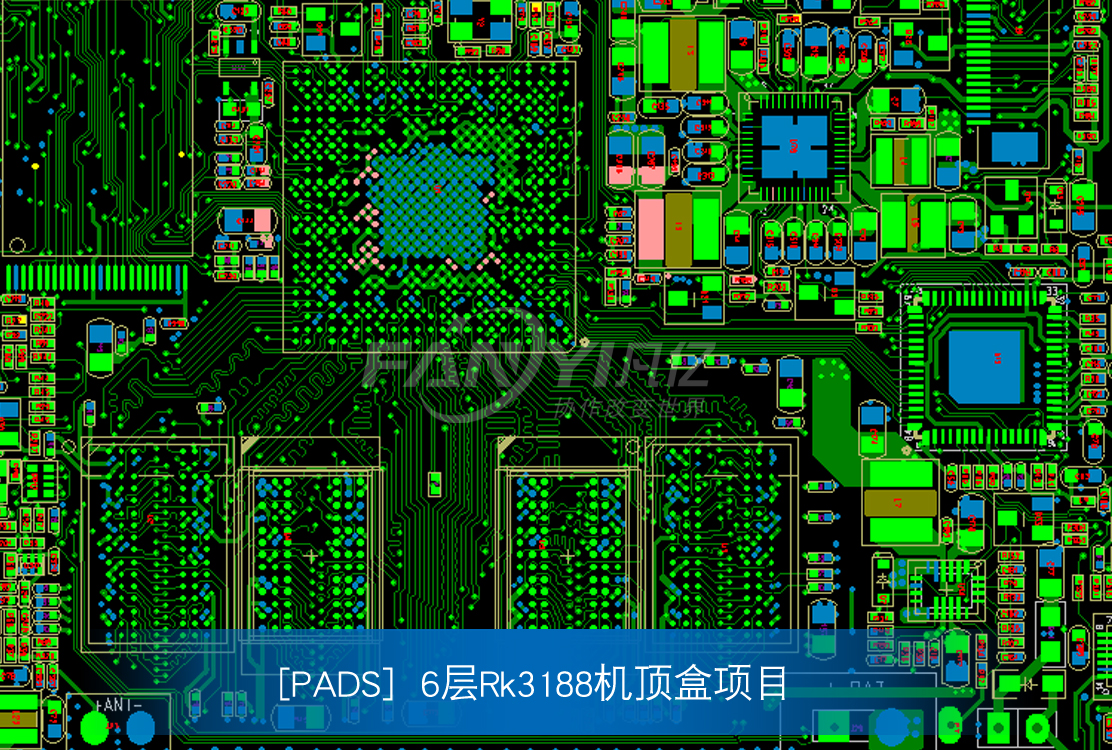

随着电子设备的高速化和小型化,PCB设计中的阻抗控制变得越来越重要。六层PCB板作为一种常见的多层板设计,其阻抗设计直接影响信号完整性和电磁兼容性(EMC)。本文将从六层PCB板的叠层设计、阻抗影响因素、阻抗计算方法以及优化策略等方面,详细探讨如何设计六层PCB板的阻抗。

一、六层PCB板的叠层设计

六层PCB板的叠层设计是阻抗控制的基础。常见的六层叠层结构包括以下两种:

SIG-GND-SIG-PWR-GND-SIG

这种叠层结构适合高密度设计,信号层与地层相邻,电源层与地层配对,能够提供良好的信号回流路径,降低电磁干扰(EMI)。

GND-SIG-GND-PWR-SIG-GND

适用于器件密度较低的场合,顶层和底层的地平面完整性较高,可作为屏蔽层使用,进一步降低EMI。

在设计时,应尽量减小电源层与地层之间的间距,以提高电源和地的耦合效果。

二、影响阻抗的主要因素

阻抗的设计受到多种因素的影响,包括:

线宽和线距

线宽增加时,阻抗减小;线距增大时,阻抗增大。

介电厚度

介电厚度增加,阻抗增大。

铜厚和阻焊厚度

铜厚和阻焊厚度增加,阻抗减小。

介电常数(Er)

介电常数越高,阻抗越小。

三、阻抗计算方法

阻抗的计算是设计的关键步骤。常用的阻抗计算工具包括:

SI9000 Field Solver

通过输入线宽、线距、介电厚度、铜厚等参数,计算出传输线的特性阻抗。

提供便捷的阻抗计算功能,适合快速设计和验证。

在计算过程中,应确保阻抗值符合设计要求,例如常见的50Ω特性阻抗。

四、阻抗设计优化策略

合理规划叠层结构

根据信号完整性和EMC需求,选择合适的叠层方案,确保信号层与地层或电源层相邻。

控制线宽和线距

通过调整线宽和线距,优化阻抗值,同时满足布线密度要求。

优化介电厚度和材料选择

选择合适的介电材料和厚度,以达到预期的阻抗值。

保证回流路径的完整性

设计完整的地平面,减少信号回流路径的阻抗,降低信号反射和串扰。

使用阻抗条测试

在PCB边缘设计阻抗条,用于测试和验证阻抗值的准确性。

五、总结

六层PCB板的阻抗设计是一个复杂但至关重要的过程。通过合理的叠层设计、精确的阻抗计算以及优化策略,可以有效提升信号完整性和电磁兼容性。在实际设计中,应结合具体的项目需求,灵活运用上述方法,确保设计的可靠性和高效性。